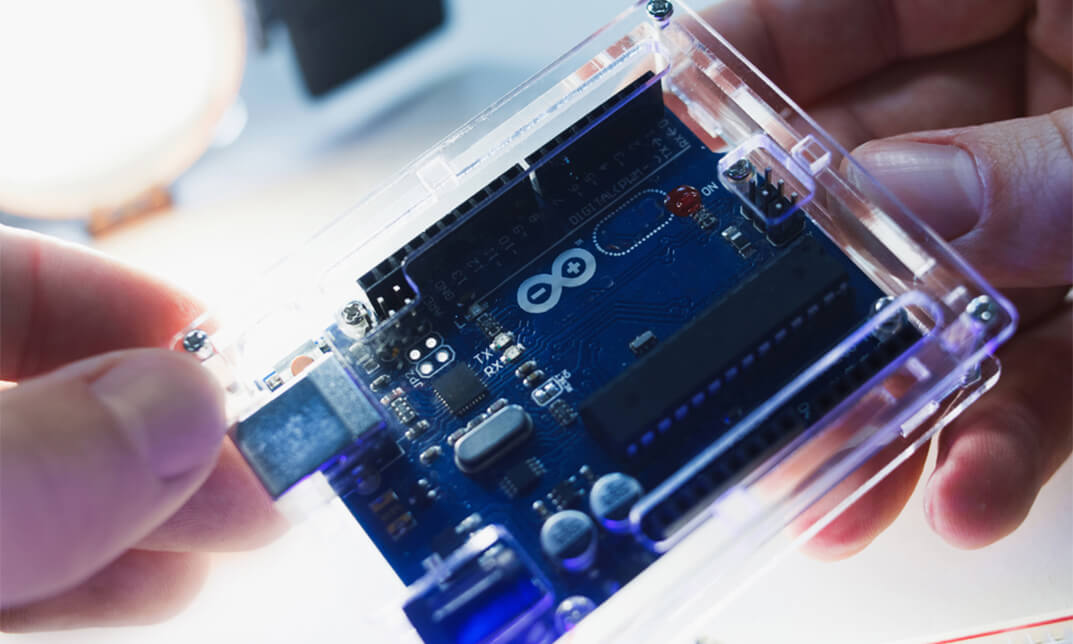

The Internet of Things promises billions of devices endowed with processing, memory and communication capabilities. These processing nodes will be, in effect, simple Systems on Chips (SoCs) and will need to be inexpensive and able to operate under stringent performance, power and area constraints. The [course_title] focuses on building SoCs around Arm Cortex-M0 processors, perfectly suited for IoT needs. Using FPGAs as prototyping platforms, this course explores a typical SoC development process: from creating high-level functional specifications to design, implementation and testing on real FPGA hardware using standard hardware description and software programming languages.

Assessment

This course does not involve any written exams. Students need to answer 5 assignment questions to complete the course, the answers will be in the form of written work in pdf or word. Students can write the answers in their own time. Each answer needs to be 200 words (1 Page). Once the answers are submitted, the tutor will check and assess the work.

Certification

Edukite courses are free to study. To successfully complete a course you must submit all the assignment of the course as part of the assessment. Upon successful completion of a course, you can choose to make your achievement formal by obtaining your Certificate at a cost of £49.

Having an Official Edukite Certification is a great way to celebrate and share your success. You can:

- Add the certificate to your CV or resume and brighten up your career

- Show it to prove your success

Course Credit: Open Culture

Course Curriculum

| module :1 | |||

| #1 — Introduction to FPGA and Verilog | 00:55:00 | ||

| #2 — RAM on DE2 and Cyclone | 00:55:00 | ||

| #3 — VGA control on DE2 | 00:56:00 | ||

| #4 — Diffusion limited agregation in Verilog | 00:54:00 | ||

| #5 — lab 2 audio filtering | 00:48:00 | ||

| #6 — Stack machine and compiler | 00:49:00 | ||

| #7 — DE2 Audio ADC/DAC | 00:45:00 | ||

| #8 — Digital filtering on FPGA | 00:38:00 | ||

| #9 — Digital filtering and lab 3 intro | 00:48:00 | ||

| #10 — lab3 2D wave equation | 00:51:00 | ||

| module : 2 | |||

| #11 — 2D wave equation on FPGA | 00:45:00 | ||

| #12 — 2D wave eqn and Verilog gen block | 00:42:00 | ||

| #13 — Verilog generate & Mandelbrot set | 00:47:00 | ||

| #14 — Wave eqn and NIOS2 | 00:47:00 | ||

| #15 — SOPC builder & NiosII | 00:51:00 | ||

| #16 — NoisII software | 00:48:00 | ||

| #17 — NiosII software and final projects | 00:45:00 | ||

| #18 — Final project discussion | 00:44:00 | ||

| #19 — FPGA floating point hardware | 00:51:00 | ||

| #20 — Project discussion and floating point | 00:49:00 | ||

| module :3 | |||

| Certification | 00:00:00 | ||

| #21 — Project discussion & multi-NiosII | 00:48:00 | ||

| #22 — Prime numbers and image processing | 00:27:00 | ||

| #23 — Edge detection on FPGA | 00:49:00 | ||

| #24 — Face detection | 00:43:00 | ||

| #25 — Mandelbrot and sound localization | 00:51:00 | ||

| #26 — Sound localization and sound synthesis | 00:42:00 | ||

| #27 — Sound synthesis | 00:51:00 | ||

| #28 — Stack machine VGA interface | 00:44:00 | ||

| Assessment | |||

| Submit Your Assignment | 00:00:00 | ||

Course Reviews

No Reviews found for this course.